PCI-SIG发布CopprLink线缆规范 适用于PCIe 5.0和6.0标准

发布时间:2024-5-5 10:34

发布者:eechina

|

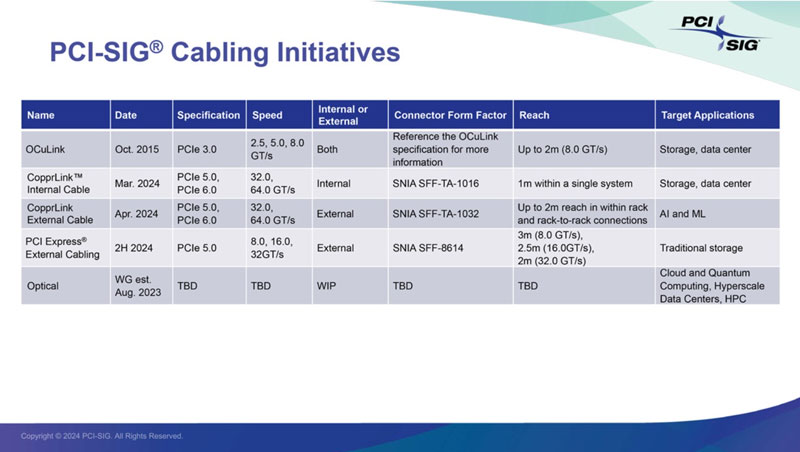

来源:EXPreview 去年11月,PCI-SIG在美国丹佛科罗拉多会议中心举行了SC23会议,向成员展示了PCIe技术演示和新的PCI快速线缆命名方案,强调了PCIe技术是高性能计算互连的首选。PCI-SIG表示,PCIe内部和外部线缆新命名方案为“CopprLink”,相关规范正在制定当中,将满足PCIe 5.0和PCIe 6.0标准的使用要求。 现在PCI-SIG终于发布了CopprLink内部和外部线缆规范,适用于PCIe 5.0和PCIe 6.0标准,提供了32/64 GT/s的信号传输速率,并利用了由SNIA维护的成熟行业标准连接器外形尺寸。PCI-SIG原来打算在2023年内发布,已经晚了小半年了。

PCI-SIG总裁兼主席Al Yanes表示,CopprLink线缆规范将PCIe布线与PCIe电气基础规范无缝集成,提供了更长的通道覆盖范围和拓扑灵活性。CopprLink线缆旨在与相同的连接器外形尺寸一起发展,适应未来PCIe技术的发展,并满足新兴应用的需求。 CopprLink内部线缆规范: · 支持PCIe 5.0/6.0标准的信号,速率分别为32/64 GT/s · 包括SNIA SFF-TA-1016连接器外形尺寸 · 单个系统内的最大传输距离为1米 · 实施示例包括独立服务器平台节点中的主板到扩展卡、主板到背板、芯片到芯片以及扩展卡到背板 · 目标应用包括存储和数据中心计算节点 CopprLink外部线缆规范: · 支持PCIe 5.0/6.0标准的信号,速率分别为32/64 GT/s · 包括SNIA SFF-TA-1032连接器外形尺寸 · 在机架到机架的连接中最长可达2米 · 实施示例包括分解服务器平台节点中的CPU到存储、CPU到内存、CPU到加速器、以及CPU到服务器平台节点中的加速器结构 · 目标应用包括存储和数据中心AI/ML用例 CopprLink内部和外部线缆规范资料已经提供给PCI-SIG成员下载,同时针对128 GT/s的PCIe 7.0 标准的CopprLink线缆相关工作已经在进行当中,这表明了PCI-SIG对CopprLink线缆规范的承诺。 |

网友评论