Altera Stratix V GX FPGAЪЕЯжСЫгыPCIe Gen3ЕФМцШнЃЌУћСаPCI-SIG IntegratorsУћТМ

ЗЂВМЪБМфЃК2013-5-23 13:47

ЗЂВМепЃКeechina

|

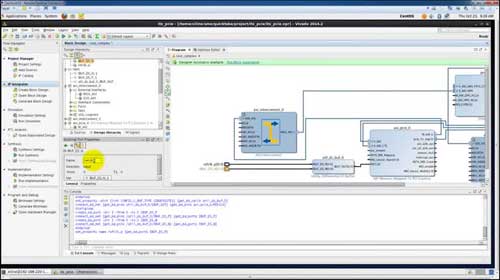

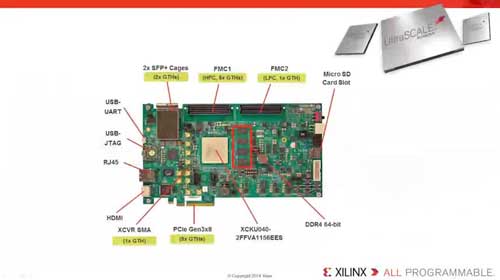

ЯждкПЩвдЮЊStratix VКЭPCIe Gen3НтОіЗНАИЬсЙЉаТЕФAltera DMAВЮПМЩшМЦ AlteraЙЋЫО НёЬьаћВМЃЌЦф28 nm Stratix V GX FPGAвбОЪеТМдкзюаТЕФPCI-SIG IntegratorsУћТМжаЃЌЗћКЯPCI Express (PCIe) 3.0ЙцЗЖ(Gen3)вЊЧѓЁЃдкзюНќЕФPCI-SIGЪЕбщЪвВтЪджаЃЌStratix V GX FPGAГЩЙІЭЈЙ§СЫШЋВПPCI-SIGМцШнадКЭЛЅВйзїадВтЪдЃЌАќРЈStratix VдкФкЕФЫљгаШ§ДњЦїМўЖМБЛЪеТМдкPCIe IntegratorsУћТМжаЁЃCyclone VКЭArria VЦїМўКЌдк1.1 (Gen 1)КЭ2.0 (Gen2)УћТМжаЃЌAlteraШЋЯЕСа28 nmЦїМўЫљгаШ§ДњВњЦЗЯждкОљЭЈЙ§СЫPCI-SIGЕФPCIeМцШнадШЯжЄЁЃ НёЬьЭЌЪБЗЂВМЕФЛЙгаЃЌЮЊТњзуStratix VПЭЛЇЮоЗьПьЫйЩшМЦPCIe Gen3НтОіЗНАИЕФашЧѓЃЌПЊЗЂСЫAlteraжБНгДцДЂЦїЗУЮЪ(DMA)ВЮПМЩшМЦЁЃStratix V GX FPGAЮЊPCIe Gen3гІгУЬсЙЉСЫдіЧПавщеЛЃЌетаЉгІгУЖдДјПэвЊЧѓЗЧГЃИпЃЌвЊЧѓвдНЯЕЭЕФГЩБОКЭзмЙІКФЪЕЯжЯЕЭГМЏГЩЃЌЬсИпСщЛюадЁЃ AlteraВњЦЗгЊЯњзЪЩюзмМрPatrick DorseyЦРТлЫЕЃКЁАStratix V FPGAБЛPCIe Gen 3 IntegratorsУћТМЪеТМБэУїЮвУЧЕФИпадФмЦїМўЗЧГЃГЩЙІЁЃИпадФмStratix VКЭPCIe Gen3ФмЙЛвЛЦ№ЮоЗьЙЄзїЃЌашвЊЫќУЧЕФПЭЛЇЯждкПЩвдГфТњаХаФЕФЩшМЦЯЕЭГЁЃДЫЭтЃЌЮвУЧаТЕФDMAВЮПМЩшМЦМђЛЏВЂМгЫйСЫИпадФмPCIe Gen3x8гВМўЕФПЊЗЂЁЃЁБ Altera DMAВЮПМЩшМЦжиЕуЭЛГіСЫашвЊPCIe Gen3x8ЕФStratix VЩшМЦЕФЙІФмЁЃЭЈЙ§еЙЪОРэТлзюДѓЗхжЕДјПэЃЌВЮПМЩшМЦБэУїAlteraЕФGen3НтОіЗНАИМИКѕФмЙЛЪЕЯжGen3ЯЕЭГЕФШЋВПДјПэЃЌЛђепGen3Ъ§ОнЫйТЪЁЃЖјЧвЃЌЭЈЙ§еЙЪОИпДя11 GB/УыЕФЭЌЪБЖС/аДВйзїЃЌЩшМЦЯдЪОСЫПЭЛЇдкЪЕМЪЪЕЯжЪБФмЙЛЪЙгУЖрДѓДјПэЁЃDMAВЮПМЩшМЦЕФЬиадАќРЈЃК • гыЪЕР§ЩшМЦвЛЭЌЙЄзїЕФLinuxЧ§ЖЏ • ЗхжЕЭЬЭТСП(250MHzЪБЃЌ256ЮЛ142жмЦк) • 7.1 GB/sЃКБГППБГTxДцДЂЦїаД256зжНкИКди • 7.0 GB/sЃКБГППБГRxЖСЭъГЩЭЬЭТСП • ЭЌЪБЖС/аДВйзїЃК11.4GB/Уы УцЯђPCIe Gen3ЕФAltera Stratix V GX FPGA Stratix V FPGAОпгаЫФИігВКЫPCIe Gen3x8жЊЪЖВњШЈ(IP)ФЃПщЁЃPCIe Gen3 IPФЃПщжЇГжx1ЁЂx2ЁЂx4КЭx8ЭЈТЗХфжУЃЌУПИіЭЈТЗДЋЫЭЫйТЪИпДя8-GbpsЃЌгыЧАвЛАцБОЕФGen2 x8ЯрБШЃЌЪЙгУGen3 x8ЭЈТЗЃЌЭЬЭТСПЬсИпСЫСНБЖЁЃгыЯргІЕФШэКЫЪЕЪЉЗНАИЯрБШЃЌStratix V FPGAжаЕФPCIe IPгВКЫФЃПщНкЪЁСЫ100,000ЖрИіТпМЕЅдЊЁЃгВКЫPCIe Gen3 IPФЃПщНЋPCIeавщЖбеЛЧЖШыЕНFPGAжаЃЌАќРЈСЫЪеЗЂЦїФЃПщЁЂЮяРэВуЁЂЪ§ОнСДТЗВуКЭЛсЛАВуЁЃStratix V FPGAЕФPCIe Gen3 IPУцЯђPCIeЛљБОЙцЗЖRev 3.0ЁЂ2.xКЭ1.xЁЃ AlteraЬсЙЉЦфШЋЯЕСаВњЦЗШЋУцЕФPCI-SIGМцШнНтОіЗНАИЃЌетаЉВњЦЗОЙ§гХЛЏТњзуСЫЙиМќгІгУашЧѓЁЃетаЉНтОіЗНАИАќРЈжЇГжЖЫЕуЁЂЧХНгЁЂНЛЛЛКЭИљЖЫПкЙІФмЕФПЩХфжУPCIe IPФкКЫКЭПЊЗЂАхЁЃ ЙЉЛѕаХЯЂ Altera Stratix V GX FPGAФПЧАвбОПЊЪМГЩЦЗЗЂЪлЁЃQuartus IIШэМў13.0АцЯТдижаЬсЙЉDMAВЮПМЩшМЦЁЃ ШчЙћгаЦфЫћЮЪЬтЃЌЛђепашвЊСЫНтЖЉЙКаХЯЂЃЌЧыСЊЯЕФњЕБЕиЕФAlteraЯњЪлДњБэЛђепЪкШЈДњРэЩЬЁЃ |

ЭјгбЦРТл