|

1 评估板简介 - 基于TI OMAP-L138(定点/浮点DSP C674x+ARM9)+ FPGA处理器的开发板;

- OMAP-L138是TI德州仪器的TMS320C6748+ARM926EJ-S异构双核处理器,主频456MHz,高达3648MIPS和2746MFLOPS的运算能力;

- FPGA采用中科亿海微eHiChip 6家族EQ6HL45系列芯片,或Xilinx Spartan-6系列芯片XC6SL16,可升级至XC6SL45。(亿海芯EQ6HL45 CSG324 pin-to-pin Xilinx Spartan-6系列XC6SLX9、XC6SLX16、XC6SLX25、XC6SLX45);

- TI OMAP-L138作为主处理器,实现操作系统运行、算法处理、指令控制等功能;

- FPGA作为协处理器,实现并行采集、外部信号处理、接口转换等功能;

- OMAP-L138和FPGA通过EMIF、SPI或UPP等接口通信,通信速度可高达228MByte/s;

- 开发板引出丰富的外设,包含1路CAN、2路RS485(其中1路RS485/422复用)、2路RS232、2路网口(1路百兆、1路千兆)、1路ADC、2路DAC、数码管、SATA、TF/SD、USB OTG、4个USB 1.1 HOST、UART、RTC、LCD等接口,同时也引出MCASP、MCBSP、uPP、SPI、EMIFA、I2C等接口,方便用户扩展。

图3 核心板背面图

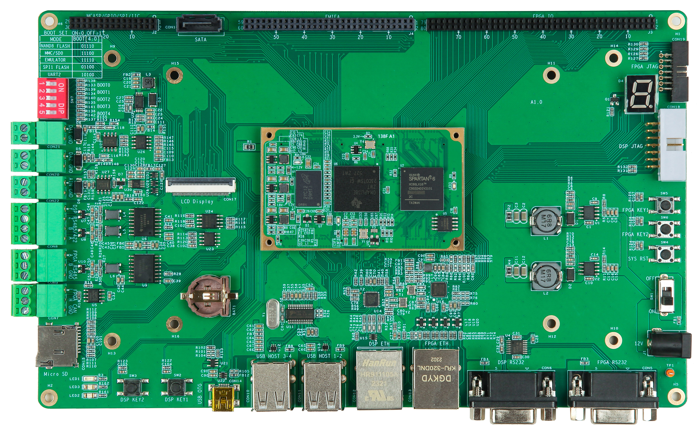

图4 L138 + EQ6HL45正面图

图5 L138 + Spartan-6正面图

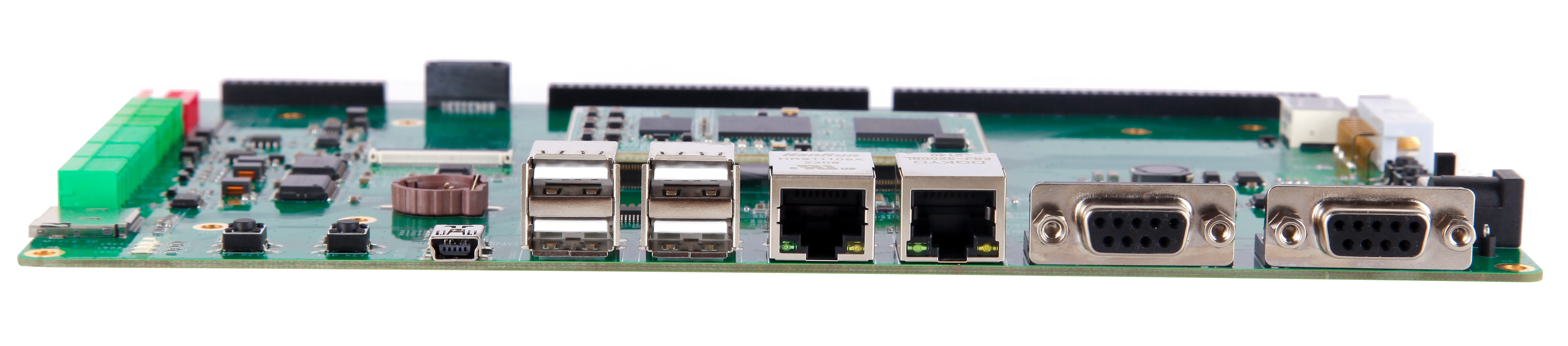

图6 开发板正面图 图7 开发板侧视图 图8 开发板侧视图 图9 开发板侧视图 图10 开发板侧视图 XQ138F-EVM是广州星嵌电子科技有限公司基于SOM-138F核心板(OMAP-L138+FPGA)开发的DSP+ARM+FPGA三核开发板,采用沉金无铅工艺的4层板设计,它为用户提供了SOM-XQ138F核心板的测试平台,用于快速评估SOM-XQ138F核心板的整体性能。 SOM-XQ138F引出CPU全部资源信号引脚,二次开发极其容易,客户只需要专注上层应用,大大降低了开发难度和时间成本,让产品快速上市,及时抢占市场先机。 不仅提供丰富的Demo程序,还提供详细的开发教程,全面的技术支持,协助客户进行底板设计、调试以及软件开发。用户可以进行项目前期的验证和评估,也可以直接用来开发自己的产品。 2 典型应用 图像处理设备 工业控制 智能电力系统 手持检测仪器 音视频数据处理 高精度仪器仪表 数据采集处理显示系统 中高端数控系统 通信设备 医疗电子设备 惯性制导... 3 软硬件参数 图11 开发板硬件资源框图 图12 OMAP-L138资源图 图13 Xilinx Spartan-6 FPGA基础参数 图14 亿海神针系列FPGA产品表 图15 亿海芯系列FPGA的基础参数 3.1 硬件性能 表1 CPU | TI OMAPL138(TMS320C6748+ARM926EJ-S),频率最高达456M | | 中科亿海微eHiChip 6家族EQ6HL45LL-2CSG324G | 或Xilinx Spartan-6系列XC6SLX16/XC6SLX45 | | | | 512MB工业级NAND FLASH,用于DSP存储 | 64Mb工业级SPI FLASH,用于FPGA配置 | | 2个80pin 0.5mm间距的母座,2个80 pin 0.5mm间距的公座 | | | | | | | | OMAPL138端1个10/100M bps自适应RJ45网络接口 | FPGA端1个10/100/1000M bps自适应RJ45网络接口 | | | | | | | | | | 1个5bit的拨码开关,用于OMAPL138启动选择 | | 4个USB 1.1 HOST接口,通过USB HUB扩展实现 | | | | 1个DSP RS232电平的串口,DB9母座 | | | | | | | | 1路ADC 精度12-bit;输入电压范围0~10V;采样率500KSPS | | 2路DAC 精度12-bit,数字编码值范围0~4095; 输出电压范围: ①0~8.192V(x1增益模式,支持所有数字编码(0~4095)), ②0~13.2V(x2增益模式,由于DAC限制输出不能超过VDD,故只支持部分编码(0~3300,十六进制值0~CE4),编程时需要注意); 输出稳定时间:4.5us; 用户接口:SPI接口,SPI时钟最高20MHz。 | | | | | 1个红色的LED电源指示灯LED1; 1个DSP LED灯LED2; 1个FPGA LED灯LED3; | | 1个红色的LED电源指示灯LED1; 1个DSP LED灯LED2; 1个FPGA LED灯LED3; | | 1片铁电存储器,存取速度比E2PROM更快,写操作之前无需先擦除 | | | | | | 30pin 2.0间距的母座1个,引出MCASP,MCBSP,SPI,I2C等扩展信号 | | 80pin 2.0间距的母座1个,引出FPGA IO 74个 | | 扩展接口上提供 12V、5V 供电,方便扩展外设供 | | | | |

3.2 软件参数 表2 | | | | | | | | | | | | 裸机(中断+共享内存)、DSPLINK 、SYSLINK | | |

|

网友评论