Stratix III FPGA与Xilinx Virtex-5:体系结构和性能对比

发布时间:2010-9-26 14:01

发布者:eetech

|

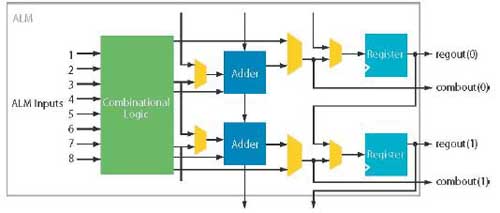

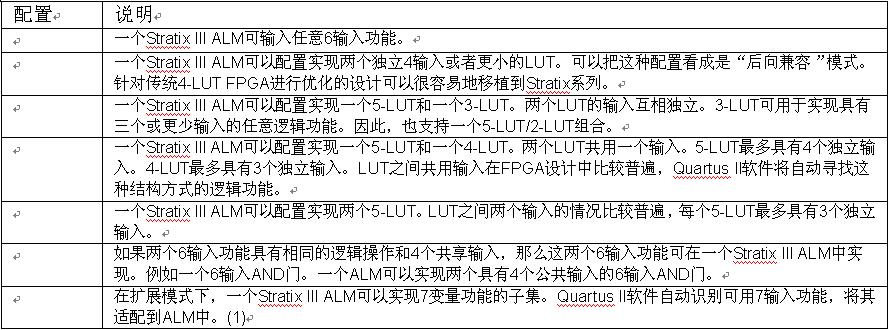

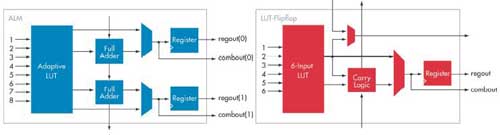

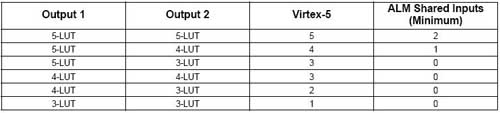

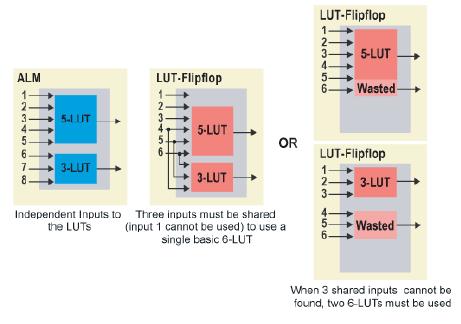

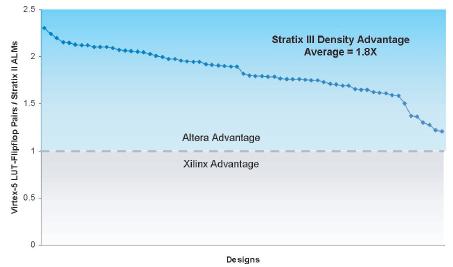

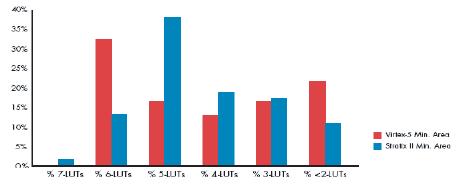

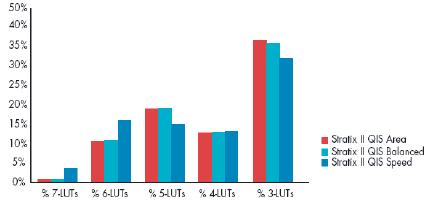

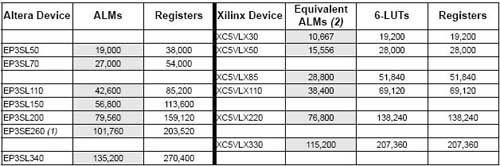

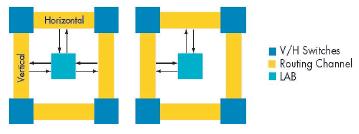

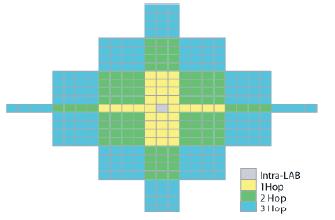

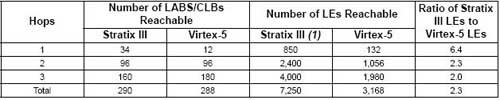

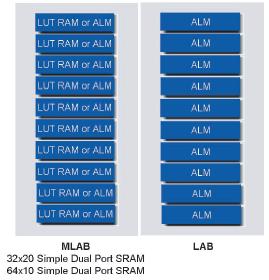

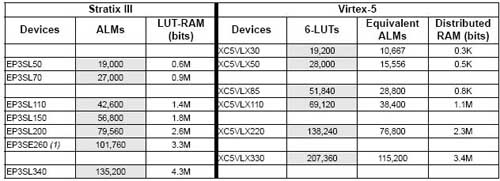

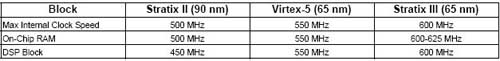

按照摩尔定律,随着工艺尺寸的降低,性能和密度在不断提高,但是却很难控制好功耗,难以跟上摩尔定律的预期。为了能够使系统级功耗保持在最低水平上,65nm Altera Stratix III FPGA采用了多种工艺技术,包括Altera专有的可编程功耗技术。Stratix III FPGA的核心结构建立在创新的逻辑单元之上——自适应逻辑模块(ALM)。这种核心结构与MultiTrack互联体系结构相结合,以很少的跳转实现高性能互联,使Stratix III器件能够以非常低的功耗,高效实现高速逻辑、算法和寄存器功能。 体系结构的优势 高性能、面积利用率非常高的体系结构的关键所在是ALM,它由组合逻辑、两个寄存器和两个加法器构成,如图1所示。组合部分含8个输入,包括一个查找表(LUT),使用Altera获得专利的LUT技术,查找表可以在两个自适应LUT (ALUT)之间进行划分。一个完整的ALM可实现一个任意6输入功能,但是由于组合逻辑模块有8个输入,因此,一个ALM可以实现两个功能的各种组合。  图1. ALM模块结构 除了能够实现一个完整的6输入LUT,ALM还可以实现两个独立的4输入功能,或者输入都独立的一个5输入和一个3输入功能(表1总结了ALM所支持的组合逻辑配置)。由于可以提供两个寄存器和两个加法器,ALM能够灵活地实现标准4输入LUT (4-LUT)体系结构的2.5个逻辑单元(LE),这一体系结构含有一个4-LUT,进位逻辑和一个寄存器。 f 关于这一体系结构的详细说明,请参考Stratix III器件手册www.altera.com/literature/hb/stx3/stratix3_handbook.pdf。 表1. 灵活的ALM  注释: (1) 请参考Stratix III器件手册(www.altera.com/literature/hb/stx3/stratix3_handbook.pdf),了解一个ALM可实现的7输入类型的详细信息。 ALM还含有两个寄存器和两个加法器,如图2所示。之所以增加了另一个寄存器,是因为实验表明,许多客户应用需要的寄存器和LUT比高于1:1。两个额外的加法器是为了增强ALM的算术能力,每个ALM可实现两个2位加法或者两个3位加法。因此,ALM要比基本6-LUT的寄存器多一倍,算术能力也提高一倍,是非常优异的构建模块。 ALM在两年前推出,要比最近才推出的Xilinx Virtex-5逻辑单元(也称为LUT触发器对)更灵活,面积利用率也更高。Virtex-5逻辑单元含有一个基本6-LUT、进位逻辑和一个寄存器,如图2所示。作为对比,ALM的组合逻辑部分有8个输入,支持所有的6输入功能,以及其他使用两个输出的大量小功能组合。Virtex-5逻辑单元的组合逻辑部分是基本6-LUT,也有64位CRAM,以及两个输出,这和ALM相似,但是只含有6个输入,实现一个以上逻辑功能的能力有限。其输出之一是6-LUT的输出,另一个是5-LUT,对应RAM配置的下半部分。  图2. Stratix III ALM和Virtex-5 LUT触发器对的对比 尽管基本6-LUT能够实现两个更小的功能,但通常还是只用作一个6-LUT。由于LUT只有6个输入,所需的共享输入数量严格限制了可组合的功能类型。这一限制使得很难将基本6-LUT用作两个5-LUT。作为对比,Stratix III ALM的两个附加输入使其能够用作两个全功能5-LUT,在面积上有很大的优势。 表2给出了几种功能组合所需要的共享输入的数量。例如,ALM能够实现两个独立的4输入功能(没有共享输入),而Virtex-5 LUT需要三个共享输入。图3是另一个例子:ALM能够实现一个5输入和一个3输入功能,不需要任何共享输入,而Virtex-5 LUT需要三个共享输入。很难找到适合Virtex-5 LUT的功能,导致输入少于6个的功能需要占用6-LUT资源才能实现。 表2. Stratix III ALM和Virtex-5 LUT灵活性对比  结合8输入分段式LUT和2:1寄存器至LUT比,ALM能够高效实现两个独立功能,每个需要一个触发器,不需要共享输入或者其他资源。结果,在任何实际设计中,所需要的ALM要少于Virtex-5逻辑单元(参见图3)。  图3. Stratix III ALM和Virtex-5 LUT触发器对实现的5输入和3输入功能 性能基准测试 Altera在65个真实设计(针对最小面积进行了优化)基础上进行了新的性能基准测试,以比较Stratix III和Virtex-5的性能。性能基准测试提供了Altera ALM和Xilinx LUT触发器对的相对性能平均测量结果。由于具有高效的分段式能力,Stratix III ALM性能平均要比Virtex-5 LUT触发器对高1.8倍。在某些设计中,甚至达到2.3倍,如图4所示。“1”处的水平黑线表示在这一点,Virtex-5 (LUT触发器对)和Stratix III (ALM)的逻辑单元数量相同。  图4. Stratix III ALM和Virtex-5 LUT触发器对性能基准测试对比 注释: (1) 在最新版ISE设计软件中,针对面积进行优化时,75个客户设计中的10个出现了错误。 为了更好的理解这些结果,图5显示了由综合产生的LUT分解。图表清晰的显示,Virtex-5器件经过综合,比Stratix III器件产生了更多的6-LUT百分比——32%比13%。这一不同的原因在于,当Virtex-5使用一个基本6-LUT时,由于大部分情况下,不管一个功能需要6个输入还是更少的输入,都要占用整个LUT,因此,Virtex-5需要尽可能多的输入。Virtex-5只能高效实现6-LUT,所以,综合总是尝试产生尽可能多的6-LUT。因为不太可能将两个功能合在一起,共享输入,因此很难建立更小的功能。  图5. 综合期间产生的LUT规模分布 由于LUT具有分段能力,综合工具可以改变LUT规模的分布,产生大小功能合适的组合,因此可以使用更少的ALM。特别是5个以及更少输入的功能只使用一半ALM,因此,只在对速率要求高的逻辑中使用6输入功能便显得非常重要。 ALM可以通过软件优化来灵活地实现。图6所示为Quartus II集成综合(QIS)针对三种不同目的(速度、面积和二者平衡)进行优化后产生的三种LUT规模分布。目的不同,LUT规模组合也就不同。当针对速度进行优化时,产生的6-LUT数量最多;针对面积进行优化时,以最少的ALM产生不同的分布。这种灵活性只有Altera能够提供,它源自在体系结构开发过程中,为获得最佳结果,对软件和硬件相互作用进行的深入研究。 f 关于ALM设计和研究的详细说明,请参阅Stratix II FPGA体系结构白皮书www.altera.com/literature/wp/wp-01003.pdf。  图6. QIS产生的功能分布 在真实客户设计基础上进行大量基准测试分析,并针对最小面积实施完整的综合、布局布线设计流程后发现,Stratix III ALM“等价于”或者“容纳的逻辑是”Virtex-5逻辑单元的1.8倍(参见表3)。 表3. 归一化后的相对逻辑性能  考虑到这一1.8倍的因素,EPSL340器件的逻辑要比XC5VLX330多出17%(参见表4和图7)。 表4. Stratix III和Virtex-5等价器件对比   图7. Stratix III L和Virtex-5 LX逻辑性能对比 注释: (1) 在这一器件密度上,EP3SE260提供最佳的逻辑、DSP和存储器。 (2) Virtex-5 6-LUT转换至ALM计数时,使用1.8倍因子。 布线体系结构 除了逻辑模块结构之外,另一关键FPGA特性是布线体系结构。Stratix系列器件引入了MultiTrack互联,以实现最佳连接和性能。布线体系结构提供不同逻辑模块群——逻辑阵列模块(LAB)之间的连接,可以通过从一个LAB到另一个LAB的“跳数”对其进行衡量。跳数越少,模式预测性更好,那么性能也就越好,CAD工具也就更容易进行优化。 布线结构是大量的行列连线。Stratix系列使用三侧布线结构,如图8所示。这意味着,一个LAB能够驱动上面一个水平通道(H)和左侧、右侧两个垂直(V)通道的所有连线,也可以接受这些通道的驱动。通道中含有长度为4、8、16和24的连线,在连线上任意LAB处都可以下载信号。  图8. 布线体系结构侧面的数量 为简单起见,只考虑长度为4的连线,图9显示了从给定LAB(灰色框表示其位置)连接至其他LAB所需要的跳数。  图9. Stratix系列连接 由于可配置逻辑模块(CLB)能够连接至一个垂直通道和一个水平通道(连接至CLB上面一半的连线,以及CLB下面一半的连线)的所有连线,因此Virtex体系结构使用两侧走线体系结构。此外,其连线只能连接至走线部分点的CLB。这些因素限制了连接和布局。采用Virtex-5器件,CLB仍能连接至两个通道,但还是需要L形(在Xilinx材料中指对角)连线来提高互联能力。 表5对比了在给定跳数情况下,Stratix III系列和Virtex-5能够连接的LAB/CLB数量。在Stratix III器件中,与Virtex-5中的CLB相比,一跳能够到达更多的LAB (34)。如果利用高效的ALM来调整这些数量,结果对Stratix III器件更有利。由于LAB含有等价的25个基于4-LUT的LE,而Virtex-5大约为11个(使用1.8倍因子),如果我们根据这些因素调整在给定跳数内能够到达的逻辑数量,就逻辑性能而言,走线连接情况会更好。 表5. Stratix III和Virtex-5连接对比  注释: (1) 1个ALM = 2.5个LE,每个LAB = 10个ALM 存储器LAB Stratix III FPGA由LAB构成,每个LAB含有10个灵活的ALM,而ALM可配置实现逻辑功能、寄存器功能以及复杂的算术功能。 Stratix III FPGA内核中增加了一种新的LAB——存储器LAB (MLAB)。LAB和MLAB是Stratix III FPGA中的共存对,MLAB ALM可用作普通的LAB ALM,也可以配置为双端口静态随机访问存储器(SRAM),如图10所示。  图10. Stratix III MLAB LAB的这种LUT-RAM功能可支持最大640位,配置为64×10或者32×20简单双端口SRAM模块,而Virtex-5的CLB只支持64×4配置。SRAM模块经过优化,可以实现滤波延迟线、小容量FIFO缓冲和移位寄存器,最大性能达到650MHz时钟速率。表6对比了Stratix III和Virtex-5系列对应器件,EP3SL340有4.3Mbits的LUT-RAM。 表6. Stratix III和Virtex-5器件的RAM分布  性能优势 Stratix III性能优势包括其独特的内核体系结构以及低功耗技术,内核体系结构可保证系统级时序逼近有足够的性能余量。 内核性能 采用Quartus II开发软件中全集成的内核体系结构,可以轻松实现Stratix III器件(该器件是业界速度最快的FPGA)的高性能优势,对设计进行最佳综合,成功实现布局布线,尽快达到时序逼近,帮助设计人员提高效能,同时达到性能目标。 图11显示了来自一组75个真实客户设计的基准测试结果,表明Stratix III器件要比Stratix II器件平均快25%。  图11. Stratix III和Stratix II基准测试 此外,Stratix III FPGA比竞争65nm器件(例如Virtex-5,参见图12)快出一个速率等级。这一平均性能优势基于业界认可的基准测试方法,在一组真实客户设计中使用了带有DSE和Xplorer的最新版Quartus II和Xilinx ISE设计软件,以获得最佳性能结果。  图12. Stratix III和Virtex-5基准测试 更好的系统级性能,并有余量 某些供应商任意规定速率,使用户不得不在实际中对规范进行调整,很难获得最佳性能,而Altera在规范上采取了保守的方法。设计人员使用Altera FPGA,可确保轻松实现时序逼近。例如,当Altera说明能够达到333MHz DDR2性能(例如采用Stratix II FPGA)时,实际在所有情况下,设计人员都能保证系统工作在333MHz上。事实上,用户的产品性能甚至可以达到400MHz DDR2。在另一个例子中,Stratix II FPGA在LVDS和DDR2规范上有足够的余量,超过1.25Gbps和400MHz。按照这一趋势,Stratix III FPGA将继续顺利实现系统级时序要求。 要实现更高的系统性能,不但需要很好的内核性能、片内RAM、数字信号处理(DSP)模块,而且还需要对I/O进行优化。Stratix III FPGA的DSP模块和片内RAM (TriMatrix存储器)针对最佳DSP性能进行了全面优化,能够运行在600MHz上。此外,Stratix III FPGA比目前所有的单片DSP处理器的性能高出几个数量级,每秒乘累加运算次数(GMAC)达到537吉。 TriMatrix片内存储器提供三种不同的存储器结构:640位MLAB、9Kbit块(M9K)和144Kbit块(M144K)。这些模块针对最大效率进行优化,MLAB可以放置在器件中的任何地方,非常灵活,能够支持600MHz以上的时钟速率。采用TriMatrix片内存储器和DSP模块,Stratix III器件是视频和图像处理、高速数字通信以及其他高性能DSP应用的理想选择。FPGA内核模块的性能如表7所示。 表7. Stratix III FPGA内核性能  为完善高性能内核,Stratix III FPGA采用了高性能I/O进行设计,能够与外部器件进行宽带连接。例如,Stratix III I/O外部存储器接口采用专用存储器接口电路,能够实现DDR3和QDR II+等最新的高性能存储器接口。Stratix III FPGA是目前唯一支持400MHz DDR3和QDR II+的FPGA。而且,DDR2、QDR2 II和RLDRAM II的性能在Stratix II器件基础上进一步得到了提高(表8中进行了总结)。Altera与一流供应商合作,确保用户的Stratix III FPGA能够连接最新的存储器。 表8. Stratix III FPGA I/O性能  使用这些高级特性和可定制知识产权(IP),设计人员能够迅速轻松的将多种应用集成到复杂系统中,而不用降低Stratix III FPGA的性能。 低功耗 Stratix III FPGA采用了创新的工艺和体系结构进行开发,降低了功耗,同时实现了最佳性能。其独特的低功耗技术包括:

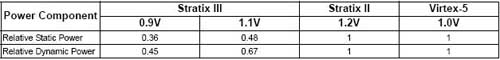

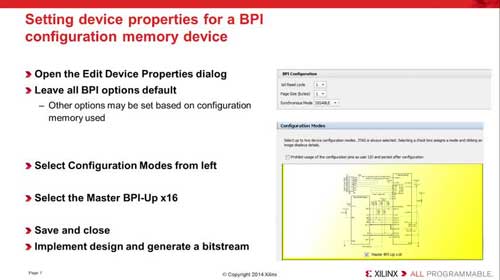

与1.2V的Stratix II FPGA和1.0V的Virtex-5相比,利用低功耗技术,Stratix III FPGA在0.9V时静态功耗降低了64%,动态功耗降低了55%(参见表9)。表9中的数值针对Stratix II进行了归一化处理,来自供应商功耗估算器工具的公开数据。计算结果基于每个ALM或者Virtex-5等价ALM的静态功耗。 表9. 高端FPGA的静态和动态功耗对比  f 关于Stratix III低功耗技术的详细说明,请参阅Stratix III可编程功耗白皮书www.altera.com/literature/wp/wp-01006.pdf。 基准测试方法 对FPGA性能进行基准测试是一项复杂的任务,不完善的测试过程会导致结果不确定或者不正确。Altera进行了大量投入以开发严谨科学的基准测试方法,并得到了业界专家的认可,是测量FPGA性能可靠正确的方法。 f 关于基准测试方法的详细信息,请参考FPGA性能基准测试方法白皮书www.altera.com/literature/wp/wpfpgapbm.pdf。 结论 由于很难控制好功耗,现在越来越难以跟上摩尔定律的预期——工艺尺寸不断降低,性能和密度不断提高。但是,经过多年的研究,Stratix III FPGA取得了多项创新,例如ALM和布线体系结构、嵌入式功能(DSP和RAM)、高级I/O标准以及外部存储器接口等。这些创新特性集成在业界领先的Quartus II软件中,能够以极低的功耗提供优异的性能,在尽可能小的FPGA中实现大型设计。 详细信息

|

网友评论