ASIC技术成FPGA杀手锏?赛灵思UltraScale架构解析

发布时间:2013-7-17 16:16

发布者:eechina

|

在先进系统中取代ASIC一直是FPGA厂商的口号。这些年来,FPGA也的确在逐步蚕食ASIC市场。那么,如果有一家FPGA厂商声称其技术优势是采用了ASIC技术,你是否会感到惊奇? 本月,FPGA巨头赛灵思宣布其首款20nm器件开始投片,而其20nm和将来16nm器件的优势是采用“ASIC级可编程架构”的UltraScale,即在完全可编程的架构中应用最先进的ASIC技术。 赛灵思和Altera总是这样。只要一家宣布了一项技术突破,不久另一家就会召开新闻发布会。实际上,过去两家在各个工艺节点上通常是交替领先,谁也甩对方不了多远。但这次赛灵思试图打破这个规律,它要在20nm节点继续领先。 FPGA的技术突破主要源于两个因素:工艺和架构。在20nm节点,赛灵思和Altera都委托台积电来生产,而且采用相同的半导体工艺。在此情况下,更合理的架构就成了致胜的唯一法宝。 上月,Altera宣布其下一代中端器件Arria 10 FPGA将采用台积电的20nm工艺(最高性能的Stratix 10则采用英特尔的14nm工艺),而且声称其优越的架构“为中端可编程器件设立了新标杆”。但我们没有获知该架构的详细信息。本月,赛灵思宣布其首款20nm器件开始投片,而其宣传的亮点则是“ASIC级可编程架构”UltraScale。 Xilinx公司全球高级副总裁汤立人 (Vincent Tong)对这个“行业首个ASIC级可编程架构”信心满满,声称赛灵思的20nm All Programmable器件将比同类竞争产品提前一年实现1.5至2倍的性能和集成度。 汤先生说,UltraScale将消除海量数据流和智能处理的瓶颈问题,而头号瓶颈就是芯片内的互连。 如下图所示,FPGA器件内的逻辑单元数量增速一直超过布线通道数量的增速。布线通道数以线性级增长,而逻辑单元数则以指数级增长。只有增加真实有效的布线通道才能应对不断增加的复杂性,实现更高的利用率。UltraScale借鉴了ASIC的互连设计,更多的快速通道布线像立交桥那样保证数据流的畅通。

逻辑单元增速超过布线通道增速

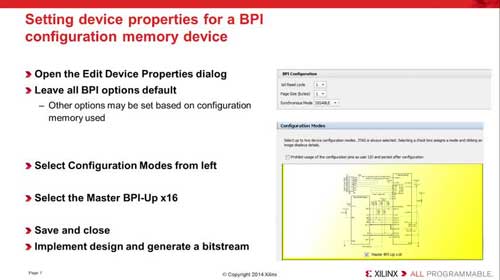

快速通道和分析协同优化弥合差距,实现超过90%的利用率 UltraScale的另一个特点是类似ASIC的时钟,它可使性能裕量最大化,实现最高吞吐量。汤先生介绍说,高速系统需要512到2048位宽度的总线,在这样的速度下有一半的时钟周期会发生时钟歪斜(skew)。UltraScale类似ASIC的时钟几乎可将时钟布置在晶片的任何地方,解决了时钟歪斜的难题。

使用较宽总线的高吞吐量系统会发生时钟歪斜

多区域、类似ASIC时钟的UltraScale时钟布线解决了时钟歪斜问题 关于更多UltraScale架构的详情,读者可参阅赛灵思公司提供的资料:Xilinx UltraScale架构 — 业界首款ASIC级All Programmable架构解决互连的瓶颈或访问 china.xilinx.com/ultrascale。 赛灵思这个采用ASIC技术他山之石的UltraScale架构似乎不仅可以用来“攻玉”(与FPGA厂商竞争),用它来“攻石”(与ASIC竞争)也许更加顺手。据汤先生介绍,赛灵思UltraScale将用于各种高性能Smarter系统,包括线路卡、桥接器等通信设备,而这些领域以前都是ASIC的地盘。事实上,赛灵思在通信市场的Design Win中有40%左右过去采用的是ASIC。采用ASIC 技术的UltraScale器件大概是ASIC厂商的又一个坏消息。 前面我们提到,赛灵思和Altera在各个工艺节点总是交替领先。UltraScale架构的出现使得赛灵思在20nm节点有机会继续领先。不过,Altera也有杀手锏,那就是英特尔的14nm工艺,一般认为它比同行要领先一两年的时间。而且Altera 14nm器件的推出时间也晚不了多少;Altera说它将于2013年提供14 nm Stratix 10 FPGA测试芯片。当然,两家的竞争对电子行业总是好消息,他们不仅给我们带来更高性能的器件,也为我们不断进军半导体制造的新领域开拓了道路。 |

网友评论